Reducing Time-to-Market with Efficient ASIC Validation

Streamline ASIC validation for faster market entry.

Accelerate Your ASIC Success with Smart Validation Strategies

Bringing an Application-Specific Integrated Circuit (ASIC) from concept to market is a high-stakes race. Every delay translates to lost opportunities and increased costs. The secret to speeding up this journey? Efficient ASIC design, verification, and validation. When done right, these steps can significantly reduce time-to-market without compromising quality or performance.

Let’s explore how a streamlined validation process can help you gain a competitive edge.

The Role of ASIC Design, Verification, and Validation in Speeding Up Time-to-Market

The journey of an ASIC doesn’t end with design. ASIC design, verification, and validation form the backbone of the development cycle, ensuring the final chip meets specifications, performs optimally, and is free of critical bugs. A well-executed validation process prevents last-minute surprises and costly re-spins.

Here’s a breakdown of how each phase contributes to faster market entry:

1. Optimized ASIC Design: Laying the Right Foundation

- Choosing the right architecture from the start minimizes redesign efforts.

- Leveraging reusable IP blocks speeds up development.

- Early detection of design flaws avoids costly delays later.

2. Verification: Catching Bugs Before They Escalate

- Running extensive simulations identifies functional issues early.

- Implementing formal verification ensures compliance with design intent.

- Automation tools reduce manual effort and improve efficiency.

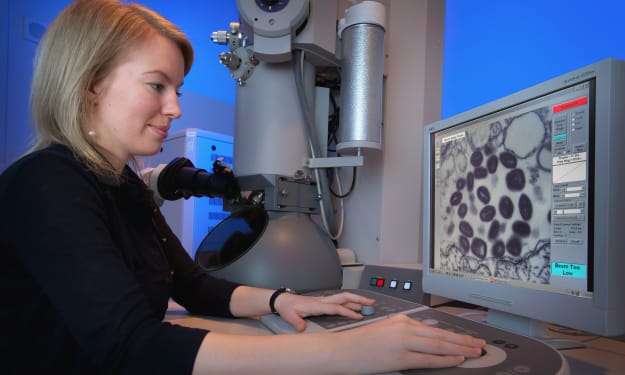

3. Validation: Ensuring Real-World Performance

- FPGA prototypes enable quick performance testing.

- Hardware-in-the-loop validation detects integration issues.

- Post-silicon validation confirms the ASIC works as expected in its final environment.

Best Practices for Faster ASIC Validation

1. Start Validation Early

Delaying validation until post-silicon stages is a recipe for slowdowns. Early-stage validation using ASIC design, verification, and validation techniques—such as simulation and emulation—prevents last-minute issues.

2. Leverage Automated Testing

Manual testing is time-consuming and error-prone. Automated test suites accelerate validation cycles and ensure comprehensive coverage.

3. Use FPGA Prototyping for Quick Iterations

Before committing to final silicon, FPGA prototypes allow rapid testing and refinement of design elements.

4. Optimize Power and Performance Metrics

Efficient power management and performance tuning during validation prevent costly post-production fixes.

5. Collaborate Across Teams

ASIC projects involve multiple teams—designers, verification engineers, and test engineers. Seamless communication ensures validation stays on track.

Common Challenges and How to Overcome Them

Challenge 1: Late-Stage Bugs

Solution: Early validation using rigorous ASIC design, verification, and validation strategies reduces the risk of last-minute surprises.

Challenge 2: Lengthy Debugging Cycles

Solution: Automated debug tools and structured test plans help pinpoint issues faster.

Challenge 3: Integration Complexities

Solution: Pre-silicon validation techniques, such as virtual prototyping, ensure smooth integration.

Closing Remarks

Reducing time-to-market for an ASIC isn’t just about working faster—it’s about working smarter. A structured approach to ASIC design, verification, and validation ensures efficient debugging, seamless integration, and a smooth transition from concept to silicon.

By implementing early-stage validation, automation, and collaboration, teams can stay ahead of timelines without compromising on quality. Faster, smarter validation equals a quicker route to market success.

FAQs

1. How does early validation impact time-to-market?

Early validation minimizes redesign efforts, catching potential issues before they reach costly manufacturing stages.

2. What role does simulation play in ASIC validation?

Simulation allows teams to verify functionality without waiting for physical prototypes, reducing debugging time and accelerating development.

3. Can automation improve ASIC validation efficiency?

Yes, automation reduces manual testing time, improves accuracy, and ensures faster iterations.

About the Creator

fidus Systems

For over 25 years, Fidus has been a leader in electronic product design and development, specializing in complex, high bandwidth, and low latency projects.

Comments

There are no comments for this story

Be the first to respond and start the conversation.